當(dāng)我們每天觸摸、滑動智能手機(jī),享受其流暢的操作與強(qiáng)大的功能時,驅(qū)動這一切的核心,正是一系列精密而復(fù)雜的集成電路。這些微小的芯片,堪稱現(xiàn)代電子設(shè)備的“大腦”與“心臟”。而理解它們?nèi)绾螐某橄蟮摹案拍顖D”演變?yōu)槲锢韺?shí)體,正是探索集成電路設(shè)計(jì)這一尖端科技領(lǐng)域的迷人旅程。

一、概念圖:從抽象到具體的橋梁

在智能手機(jī)中,集成電路的概念圖并非我們通常所見的產(chǎn)品外觀圖或電路板照片,而是一種高度抽象化的設(shè)計(jì)藍(lán)圖。它主要存在于設(shè)計(jì)階段,用于描述芯片內(nèi)部的功能模塊、邏輯關(guān)系、數(shù)據(jù)流向和物理布局規(guī)劃。

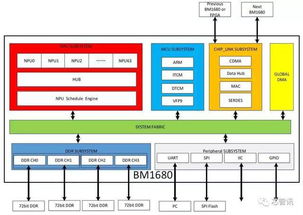

1. 系統(tǒng)級與架構(gòu)設(shè)計(jì): 在最高層面,設(shè)計(jì)師會根據(jù)智能手機(jī)的功能需求(如5G通信、AI處理、高清攝像、圖形渲染等),規(guī)劃出整個芯片系統(tǒng)的架構(gòu)。這就像為一棟摩天大樓繪制總體設(shè)計(jì)圖,決定哪里是CPU(中央處理器,負(fù)責(zé)通用計(jì)算),哪里是GPU(圖形處理器),哪里是NPU(神經(jīng)網(wǎng)絡(luò)處理器,專用于AI),以及內(nèi)存控制器、各種輸入輸出接口等模塊如何協(xié)同工作。例如,蘋果的A系列芯片或高通的驍龍芯片,其概念始于對性能、功耗、面積(PPA)三大要素的極致權(quán)衡。

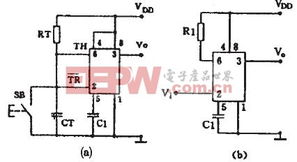

2. 邏輯與電路設(shè)計(jì): 架構(gòu)確定后,工程師會使用硬件描述語言(如Verilog或VHDL)將功能“代碼化”,生成寄存器傳輸級(RTL)描述。這一步相當(dāng)于寫出了芯片行為的具體“劇本”。通過邏輯綜合工具,將RTL代碼轉(zhuǎn)換成由基本邏輯門(如與門、或門、非門)構(gòu)成的網(wǎng)表。此時的“概念圖”表現(xiàn)為復(fù)雜的邏輯電路圖,定義了數(shù)以億計(jì)晶體管之間的連接關(guān)系。

3. 物理設(shè)計(jì): 這是將邏輯網(wǎng)表轉(zhuǎn)化為實(shí)際幾何版圖的關(guān)鍵步驟。版圖設(shè)計(jì)師需要決定每個晶體管、每條連線在硅片上的精確位置和形狀,考慮信號完整性、時序、功耗和散熱。這個過程會產(chǎn)生最終的“概念圖”——版圖,它是一張多層、極度精細(xì)的平面圖,通過光刻等工藝最終轉(zhuǎn)移到硅晶圓上。智能手機(jī)芯片的版圖設(shè)計(jì)往往需要借助先進(jìn)的電子設(shè)計(jì)自動化(EDA)軟件,在納米尺度上進(jìn)行反復(fù)仿真和優(yōu)化。

二、智能手機(jī)中的關(guān)鍵集成電路及其設(shè)計(jì)挑戰(zhàn)

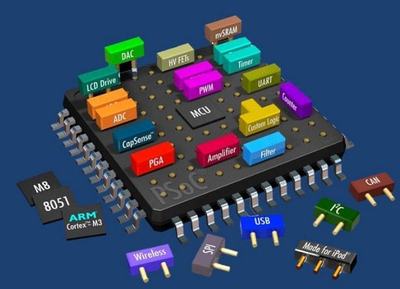

一部現(xiàn)代智能手機(jī)集成了多種專用集成電路,其設(shè)計(jì)各有側(cè)重:

- 應(yīng)用處理器(AP): 這是手機(jī)的“大腦”,設(shè)計(jì)最復(fù)雜。它采用片上系統(tǒng)(SoC)設(shè)計(jì),集成了CPU、GPU、NPU、ISP(圖像信號處理器)、調(diào)制解調(diào)器等多種核心。設(shè)計(jì)挑戰(zhàn)在于如何在一個狹小的空間內(nèi)實(shí)現(xiàn)高性能與低功耗的完美平衡,并確保各模塊高效互通。

- 內(nèi)存芯片(如LPDDR5): 設(shè)計(jì)追求極高的數(shù)據(jù)吞吐速度和更低的功耗。其概念圖圍繞著存儲單元陣列、靈敏放大器和外圍控制電路的優(yōu)化布局展開。

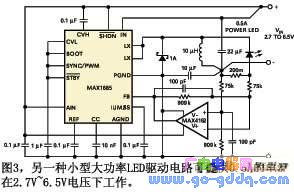

- 電源管理芯片(PMIC): 如同手機(jī)的“心臟起搏器”,負(fù)責(zé)為各個部件提供穩(wěn)定、不同電壓的電力。其設(shè)計(jì)核心是高效能的電壓轉(zhuǎn)換模塊和精細(xì)的功耗管理邏輯。

- 射頻前端模塊: 負(fù)責(zé)處理5G/4G、Wi-Fi、藍(lán)牙等無線信號。設(shè)計(jì)難點(diǎn)在于在微型化封裝中集成多個濾波器、功率放大器、開關(guān),并處理高頻信號間的干擾。

三、設(shè)計(jì)趨勢與未來展望

智能手機(jī)集成電路的設(shè)計(jì)正朝著幾個方向飛速演進(jìn):

- 先進(jìn)制程: 從7納米、5納米到3納米甚至更小,晶體管尺寸的不斷縮小,使得單位面積集成度更高、性能更強(qiáng)、功耗更低,但設(shè)計(jì)規(guī)則也愈發(fā)嚴(yán)苛,量子隧穿等物理效應(yīng)成為新的挑戰(zhàn)。

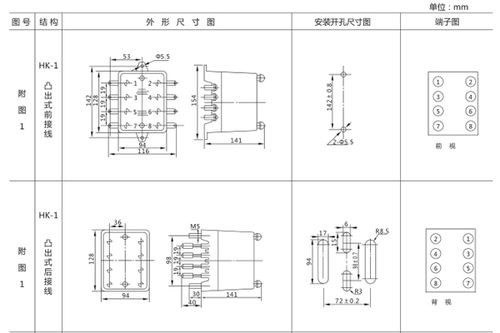

- 異構(gòu)集成與Chiplet: 由于單一芯片的物理極限和成本問題,將不同工藝、不同功能的芯片粒(Chiplet)通過先進(jìn)封裝(如3D堆疊)集成在一起,成為新的設(shè)計(jì)范式。這要求概念圖從單一的平面布局,擴(kuò)展到考慮三維互連和系統(tǒng)級封裝協(xié)同設(shè)計(jì)。

- AI驅(qū)動設(shè)計(jì): 人工智能正在變革芯片設(shè)計(jì)本身。EDA工具開始集成AI,用于自動布局布線、優(yōu)化功耗和預(yù)測性能,大幅縮短設(shè)計(jì)周期,探索人類設(shè)計(jì)師難以想象的優(yōu)化方案。

- 專用化與定制化: 為滿足智能手機(jī)特定的AI計(jì)算、影像處理需求,定制化的ASIC(專用集成電路)設(shè)計(jì)日益重要,如谷歌的Tensor核心、蘋果的神經(jīng)網(wǎng)絡(luò)引擎,它們的設(shè)計(jì)概念圖從一開始就為特定算法做了深度優(yōu)化。

###

智能手機(jī)中集成電路的概念圖,是一幅凝聚了人類頂尖智慧、從抽象構(gòu)思到物理實(shí)現(xiàn)的微觀宇宙地圖。它的每一次演進(jìn),都直接推動著手機(jī)變得更智能、更強(qiáng)大、更省電。集成電路設(shè)計(jì),這個在方寸之間進(jìn)行天文數(shù)字般復(fù)雜工程的領(lǐng)域,不僅是技術(shù)的高地,更是連接數(shù)字世界與現(xiàn)實(shí)世界的核心藝術(shù)。隨著新材料、新架構(gòu)和新設(shè)計(jì)方法的出現(xiàn),這張“藍(lán)圖”將繼續(xù)描繪出更加令人驚嘆的科技圖景,深藏于我們掌中的方寸之地。